I.9 : Petit résumé :

L'étude qui fait l'objet de ce mémoire a plusieurs caractéristiques et contraintes :

Domaine d'étude restreint, complexité initiale limitée et maitrisée (ou du moins le croit-on).

Utilisation d'une plateforme informatique répandue et économique.

Programmation "intelligente", élaborée et soignée, privilégiant tant que possible

la vitesse d'exécution aux dépends de la portabilité, de la vitesse de développement et

de la maintenabilité.

Travail de recherche sur l'adequation des algorithmes avec la plateforme pour

accélérer au maximum l'exécution, transformant complétement le modèle initial

pour cadrer au plus près avec la machine.

Interactivité avec l'utilisateur, disponibilité des résultats et utilisation du potentiel

du modèle utilisé.

Ces critères expliquent pourquoi ce projet ne ressemble pas à des projets classiques :

l'unique paramètre intéressant étant la vitesse, de nombreux problèmes étant précedemment

résolus de manière théoriques ou conceptuels, le défi à relever est la gestion de la

complexité croissante du projet.

Partie II : Présentation des Gaz sur Réseaux

II.1 : Introduction :

Cette partie ne peut pas et n'a pas la prétention d'être exhaustive : le sujet est trop vaste

pour pouvoir envisager d'en faire le tour complet. Il n'est pas non plus possible ici d'expliquer

(encore et encore) ce que sont les LGA : d'autres articles ou livres le font très bien.

Le lecteur novice et pressé peut consulter l'annexe B,

les explications les plus claires en français sont données en [18],

[14] et [27]. Ce mémoire discute de

la programmation d'un modèle physique, nous allons donc nous concentrer sur les notions essentielles

qui permettent de comprendre les choix de conception.

II.2 : Nomenclature :

Le terme de "gaz sur réseau", ou "lattice gas automata" en anglais (LGA) n'a pas fait l'objet

d'une étude par l'Académie Française et la première question est de savoir s'il faut mettre "réseau"

au pluriel. La réponse la plus satisfaisante consiste à considérer le réseau comme un médium, un

"ether" virtuel et digital sur lequel prennent vie des phénomènes, grâce au support physique de l'ordinateur.

Un "gaz sur réseau" désigne donc un gaz particulier (par exemple "FHP-3") alors que l'expression

"les gaz sur réseaux" désigne un ensemble de gaz aux propriétés différentes (par exemple l'ensemble des LGA

en deux dimensions).

On peut aussi trouver dans la littérature diverses dénominations pour désigner un ou des gaz sur réseaux :

"LGA", "LG" pour "Lattice Gas", "LGCA" pour "Lattice Gas Cellular Automata", GR ou GSR pour

"gaz sur réseau(x)"... Les nombreuses variantes des modèles apportent encore d'autres noms ou acronymes.

II.3 : Génèse :

L'existence des LGA est liée à plusieurs courants d'idées ou techniques. D'abord, les LGA sont une

simplification extrême des lois et des programmes de "Dynamique Moléculaire" où chaque particule

(atomes ou molécules) d'une matière est simulée avec sa vitesse, sa masse, sa direction, avec autant de

valeurs en virgule flottante pour chaque grandeur et dans chaque dimension. Ainsi, contrairement aux

méthodes d'éléments finis,

les particules sont simulées afin de laisser ressortir leur comportement individuel, au lieu de les

enfermer dans des moyennes et des interpolations. Les Gaz sur Réseaux se situent entre le monde

de la dynamique moléculaire ("MD") d'une part et les techniques volumiques classiques (Euler ou

Navier-Stokes par exemple) d'autre part, car ils apportent la capacité de simuler de plus grands

phénomènes qu'avec de la MD classique. Ils peuvent faire émerger des comportements de plus grande

échelle, accessibles seulement par les techniques d'éléments finis mais avec un niveau de détail

supérieur.

L'autre facteur déterminant pour l'existence des LGA est la démocratisation des ordinateurs. Il suffit

en fait de peu de ressources pour commencer à expérimenter sur ce type de "médium". C'est cette dépendance

technologique qui explique en partie l'historique de la méthode : tout comme pour les Automates Cellulaires

classiques, les premières expériences ont été réalisées à la fin des années 60 (Kadanoff & Swift, 1968)

et le premier modèle intensément étudié (HPP) date officiellement de 1973. Le domaine a ensuite explosé au

début des années 80 grâce à des ressources informatiques répandues et l'intérêt du public.

Les LGA ont des liens de parenté très forts avec d'autres modèles comme les Automates Cellulaires

classiques ou le modèle d'Ising, utilisés en thermodynamique ou pour étudier les séparations de phases

sans hydrodynamique. Le modèle HPP représente une convergence naturelle de toutes ces influences

et a créé un nouveau domaine hybride et fascinant.

II.4 : Un premier modèle : HPP

Les LGA sont issus de recherches de mécanique statistique, un des objectifs étant de simplifier les

lourds calculs de dynamique moléculaire pour en extraire les composantes fondamentales.

Des modèles à vélocité finie, à temps fini puis des simplifications

de plus en plus radicales (binarisation et discrétisation totale) ont donné le jour en 1973 au modèle dit "HPP"

[37]

(initiales de Jean Hardy, Olivier de Pazzy et Yves Pomeau). Ce modèle n'est pas utilisable en pratique mais

sa compréhension est importante pour des raisons historiques et techniques car il n'est pas possible

de faire plus simple (en deux dimensions). Il cristalise donc tous les défauts et toutes les caractéristiques que l'on

retrouve dans les modèles plus évolués et son étude permet de généraliser des techniques

aux autres modèles. Par exemple, les équations de collision ou la complexité algorithmique

(comme dans [31]) sont étudiées d'abord sur HPP avant d'être adaptées aux

autres modèles.

HPP ressemble à un Automate Cellulaire à voisinage de Von Neumann (carré) simple, synchrone et homogène.

Il diffère d'un Automate Cellulaire classique car chaque cellule ne possède pas d'état interne : comme noté précédemment,

le gaz sur réseau est un "médium" sur lequel transitent des particules booléennes qui s'entrechoquent

aux intersections du grillage. Les cellules sont ici appelées "noeuds" et sont le siège des collision.

Comme le tapis d'un billard sur lequel roulent les boules, les particules se déplacent sans friction

sur cet "ether" informatique.

Les frictions que l'on veut faire apparaitre sont du type hydrodynamique (par exemple la viscosité) et concernent les

interactions entre particules. Les interactions avec le médium servent à déterminer les "conditions aux limites"

(les parois ou les objets qui agissent sur le fluide). Les collisions entre les particules

déterminent le comportement du fluide et avec HPP il n'y a pas beaucoup de choix : les règles de conservation sont

strictes et il n'y a pas beaucoup de degrés de liberté. Ainsi :

- Toute collision doit conserver le nombre de particules : il y a autant de particules qui entrent

dans le noeud (afférentes) que de particules sortantes. Le contraire ne serait pas logique.

- Toute collision doit conserver l'impulsion générale des particules : en "clair", la somme vectorielle

des vecteurs mouvements de toutes les particules entrantes doit être identique à la somme vectorielle

des vecteurs mouvements de toutes les particules sortantes. Nous aurons l'occasion de revenir plus en détail

sur ce sujet bientôt.

- Il n'y a que 2^4 (16) configurations possibles pour chaque site. Les seuls quatre voisins limitent le nombre

de combinaisons intéressantes.

Pour simplifier, les collisions n'ont qu'un seul cas particulier : le "choc frontal". Toute autre configuration

est "transparente" et laisse les particules voyager librement. Le travail du programme de simulation HPP consiste

à faire voyager les particules d'un site à l'autre et de vérifier à chaque fois si un choc frontal a lieu.

Puisque toutes les quantités sont binaires, la complexité algorithmique est considérablement simplifiée

par rapport à un programme de Dynamique Moléculaire classique, où les collisions peuvent se produire

à tout moment. De plus, on économise tous les tests de collisions comme tous les types de calculs en virgule

flottante (potentiellement instables). Pourtant, même avec HPP, des phénomènes hydrodynamiques (plus ou moins

réalistes) peuvent apparaitre malgré la simplification extrême : le comportement à l'échelle macroscopique

ne dépend pas des propriétés microscopiques (par exemple, les mêmes lois permettent d'étudier les écoulements

d'air et d'eau). Les collisions des particules dans les Gaz sur Réseaux jouent un rôle crucial dans l'émergence

des phénomènes macroscopiques.

Parmi toutes les combinaisons possibles, le choc frontal est la seule qui permette de réorganiser les

particules afférentes tout en respectant les lois de conservation énoncées précédemment.

Description d'une collision frontale.

La conservation de masse et du nombre de particules est simple puisque les particules ont la même masse et

le nombre de particules afférentes est identique au nombre de particules sortantes (deux dans ce cas).

L'énergie du système est donc conservée. La conservation de l'impulsion (vecteur mouvement) est un peu plus délicate

à montrer, le dessin ci-dessous résume l'idée.

Description des vecteurs mouvements d'une collision frontale.

L'impulsion est la somme des vecteurs mouvements des particules. Le cas de la collision frontale avec HPP se résume

à additionner deux vecteurs (unitaires) de direction opposée, ce qui donne un vecteur nul. L'impulsion d'autres configuration

donnera d'autres vecteurs mais le choc frontal est la seule configuration où toutes les grandeurs énoncées

sont conservées et où l'on puisse avoir une autre configuration en sortie. Ce type d'échange de configuration

est la base de l'émergence de phénomènes d'hydrodynamique à l'échelle macroscopique et sera raffiné plus tard.

II.5 : Caractéristiques du modèle HPP :

Le choc frontal représente 12,5% du champ de collision (2 combinaisons sur 16) et se produit à une densité de 0.5

(2 particules sur 4). Par rapport aux modèles récents, le premier rapport montre une faible efficacité (faible

rapport de nombre de Reynolds par site) mais HPP est inutilisé surtout parcequ'il a quatre "invariants"

qui sont nuisibles dans la plupart des cas. Les "invariants" sont des quantités conservées dans le modèle

et qui ne correspondent pas au comportement d'un fluide réel.

- température : HPP est un modèle où toutes les particules ont la même vitesse. Or la vitesse

des particules (dans l'air par exemple) est fonction de leur température (et vice versa). Avec HPP la masse

de toutes les particules est identiques, donc leur énergie cinétique ne change pas. Il n'est pas possible

de simuler des transferts de chaleur ou tout phénomène où la température change : tout le fluide simulé

est à une température uniforme, homogène. Cela simplifie l'étude des équations caractéristiques mais interdit

d'explorer les pans les plus passionnants de la mécanique des fluides et de la thermodynamique.

- invariance de parité linéaire (désolé pour le néologisme) :

un phénomène curieux de non-répartition homogène est implicitement porté par HPP.

Il n'est pas possible de diffuser uniformément une masse de particules dans un fluide,

bien que la diffusion ne fasse pas apparaitre d'onde carrée prononcée.

Cela est dû au fait que la collision frontale, seule permise par le modèle,

ne traite qu'un nombre pair de particules par lignes.

Pour poser le problème simplement, on peut considérer que la parité du nombre de particules

sur une ligne ne change pas. L'effet indésirable n'est sensible qu'avec

des géométries très petites mais reste gênant car il est conservé dans les équations à grande échelle.

- anisotropisme : tout phénomène ne se produira pas de la même manière selon

l'orientation par rapport à la grille du gaz. Plus simplement, le fluide a un "axe de préférence", l'orientation

du médium agit indirectement sur le fluide. C'est un défaut majeur qui empêche d'étudier correctement des

tourbillons par exemple.

- invariance galiléenne : l'aspect monocinétique du fluide

empêche les tourbillons de se déplacer à la même vitesse que le fluide. Si un tourbillon apparait dans le

fluide, il sera advecté (emporté) plus vite que celui-ci (selon les cas).

En simplifiant à outrance la dynamique moléculaire, de nombreux "artefacts" liés à la discrétisation apparaissent.

Les équations qui régissent le fluide prennent toutefois un nouveau visage et l'expérimentation

informatique est plus facile. Depuis l'apparition de ce modèle, de nombreuses variantes ont vu le jour pour

atténuer ou éviter les problèmes présentés ici, ainsi que d'autres qui ont été découverts ensuite.

II.6 : Le modèle FHP :

Les Automates Cellulaires peuvent-ils résoudre des équations différentielles partielles, comme

celles de Navier-Stokes ?

Telle était la question cruciale posée par de nombreux scientifiques depuis l'apparition de ce domaine d'étude.

Rappelons que les premiers calculateurs automatiques ont été conçus dans cette optique, comme la machine à différences

finies de Babbage ou le calculateur électronique de John Vincent Atanasoff (1937-1942).

Stanislaw Ulam et Konrad Zuse dans les années 50, Stepen Wolfram et Richard Feynman dans les années 80, ont

milité pour résoudre cet épineux problème. Pourtant, ce n'est que dix ans après l'introduction du modèle HPP que

la connexion entre les deux sujets a été comprise. Uriel Frisch, Brosl Hasslacher et Yves Pomeau (d'où FHP)

ont proposé en 1986 une lègère modification qui permet de retrouver les équations différentielles de Navier-Stokes

[19].

La première modification du modèle HPP porte sur le "medium" anisotropique. Au lieu d'un maillage carré, un maillage

hexagonal est nécessaire et suffisant pour résoudre ce problème. Cette légère modification permet en fait d'augmenter

le nombre de degrés de liberté lors des collisions et d'avoir plus de possibilités de sortie différentes. Le

fluide a donc plus d'opportunités de diffuser ses particules dans chaque direction et de diminuer sa viscosité.

Les simulations deviennent soudain plus intéressantes ...

La deuxième amélioration du modèle HPP résoud "l'invariance de parité linéaire" en exploitant ces nouveaux

degrés de libertés. Le nombre de collisions équivalentes augmente et il suffit d'ajouter une nouvelle loi

de collision : la "collision triangulaire".

L'invariance galiléenne sera pour l'instant corrigée par un adimensionnement d'une grandeur. Si l'advection

d'un vortex a lieu à quatre fois la vitesse du fluide, on divisera par quatre les vitesses mesurées

pour retrouver l'invariance galiléenne (en monophasique). Cette méthode n'est plus valable avec différentes

phases mais cela sort du sujet du mémoire.

La température n'est pas un problème en soi, elle n'intervient pas dans les expériences qui intéressent les

utilisateurs de LGA. Si elle est nécessaire, la solution est simple : avoir plusieurs vitesses de particules.

Deux moyens existent : les particules elles-mêmes sautent plusieurs sites à chaque pas de temps, ou/et

les liens ont plusieurs longueurs. Les règles de collision doivent refléter ces changements tout en

respectant les règles de conservation initiales. En deux dimensions, un tel réseau est généralement le

voisinage de Moore à 8 voisins : les diagonales sont 1.41 fois plus longues que les liens horizontaux ou verticaux.

Le réseau hexagonal reste toutefois plus intéressant pour son plus grand nombre d'isométries et donc par un

plus grand nombre d'opportunités de collisions équivalentes (D2Q12 ?).

II.7 : Les règles et les nouvelles propriétés de FHP-1 :

Dans leur fameux article [19], Frisch, Hasslacher et Pomeau vont décrire une première

version du modèle FHP qui répond à la contrainte d'être nécessaire et suffisante pour retrouver les équations

de Navier-Stokes à grande échelle. Seule la partie théorique est résolue dans l'étude, l'efficacité

n'est pas au rendez-vous : les améliorations viendront plus tard, la démonstration étant déjà un grand pas.

Les règles de collision du modèle FHP-1.

Le deuxième effet du changement de géométrie, après avoir brisé l'anisotropie, fut d'apporter d'autres

axes de symétrie : 3 au lieu de 2. Il y en a maintenant 64 possibilités de configuration en entrée, au lieu de 16.

Les auteurs vont introduire 2 types de collisions au lieu d'une seule, soit 5 collisions au lieu de 2 pour HPP,

si on tient compte des symétries et des rotations. On passe de 12,5 % à 12,8 % d'exploitation du champ des

collisions mais l'amélioration se situe autre part.

D'abord, la collision triangulaire améliore sensiblement la qualité de l'écoulement et permet à elle seule

de faire apparaitre des comportements hydrodynamiques réalistes. Elle permet de faire "communiquer" entre elles

des lignes et de mieux répartir les particules sur les différents axes du réseaux.

Ensuite, et c'est tout aussi remarquable : les collisions frontales n'ont plus seulement une, mais deux "voies

de sortie". Il existe trois configurations d'entrée équivalentes, équiprobables, au lieu de deux pour HPP.

Il faut donc choisir, lorsqu'un choc frontal a lieu, la configuration de sortie.

- La première solution (naïve) est de fixer

statiquement un ordre : par exemple effectuer une rotation de 60 degrés pour chaque configuration.

=> Cette solution introduit un nouvel effet parasite : la chiralité, ou préférence d'un sens de rotation,

qui est néfaste lors de l'émergence de phénomènes très turbulents. Il faut éviter de favoriser une direction

autant que possible afin de garder le fluide "pur". La chiralité peut être un moyen de simuler l'effet de

Coriolis mais ce n'est pas cohérent avec notre échelle macroscopique.

- Deuxième solution, pour les programmeurs fatigués ou pressés (comme Haarlan Stockman) : changer de chiralité

une ligne sur deux. La parité du numéro de la ligne indique si le sens de rotation est de +60 ou -60 degrés.

=> Des études [d'Humières ?] ont montré que les effets de la chiralité ne sont pas totalement effacés, principalement au niveau des

parois. Ce mauvais compromis n'est pas recommandé en pratique, même si les effets ne sont pas directement visibles.

- La solution recommandée est d'effectuer la rotation une fois sur deux, au hasard. Le générateur de nombres

aléatoires n'a pas besoin d'être de qualité indiscutable, mais suffisante pour briser la chiralité. Il doit donc

simplement être équiprobable et avoir une longue période de répétition. Dans notre programme d'expérimentation,

le nombre aléatoire est tout simplement mis à jour en fonction des sites précédents (un simple ADD avec les

sites de direction A) ce qui fournit des données de nature suffisamment indépendantes pour briser la chiralité,

après une période d'amorçage négligeable.

Si les chiralités locales sont choisies chaque fois au hasard et de manière totalement indépendante, le fluide

simulé diffère d'un fluide HPP d'une autre façon encore : il devient irréversible. Alors qu'un fluide HPP

est purement déterministe (toute configuration initiale des particules donnera une unique configuration

finale) le fluide FHP peut donner un nombre quasiment infini de configurations de sorties, selon le générateur de

nombres aléatoires. Si les nombres sont "réellement" aléatoires, le fluide correspond à un fluide réel et

il n'est pas possible de remonter à la configuration d'origine après n'importe quel nombre de pas de calcul.

Pour illustrer cette propriété incroyable, on procède parfois à l'expérience suivante : soit un programme FHP

avec une configuration des particules initiales choisies arbitrairement. Le générateur de nombres aléatoires

est déterministe et réversible.

1) Le programme est lancé et calcule T pas de temps, autant que nécessaires pour

obtenir une relaxation suffisante du fluide (une soupe brownienne bien homogène).

2) Les direction des particules sont toutes inversées et le programme est relancé avec le générateur de nombres

aléatoires tournant dans le sens inverse.

3) Après un même nombre T de pas de temps, le fluide retrouve sa configuration initiale, telle qu'au début du 1).

4) Ensuite, on restaure l'état du 2) et on change un bit, une direction de particule ou la "graine" du générateur

de nombres aléatoires. Quel que soit le nombre de pas de temps de calcul, la configuration initiale ne sera pas

retrouvée et elle restera certainement à l'état de "soupe brownienne".

Christopher Moore a démontré [31] que la prédiction du résultat d'un calcul FHP fait partie

de l'ensemble P-complet. En français, cela signifie que pour obtenir le résultat de N cycles, il faut effectuer tous

les N pas de temps les uns après les autres : il n'y a pas de court-circuit possible. Il n'y a théoriquement pas de

moyen de calculer le Nième état d'un LGA sans calculer tous les états précédents. Le calcul "brut" est la seule voie

possible pour atteindre le résultat de la simulation, les optimisations doivent donc porter sur la partie de calcul.

Le fluide FHP a des propriétés fortement non linéaires et dissipatives, ainsi que de nombreuses autres

propriétés curieuses, malgré sa simplicité étonnante. Il obéit à la loi de Mariotte et des gaz parfaits.

Il est un milieu compressible et peut donc propager une onde "sonore" de manière circulaire comme dans la nature.

Son calcul est par construction inconditionnellement stable et exact.

Mais son efficacité est mauvaise en pratique : le chemin

parcouru par une particule entre deux collisions (mean free path en anglais) est très long en moyenne,

la viscosité du fluide est forte et il faut donc des millions de sites pour simuler des phénomènes intéressants.

II.8 : Les améliorations de FHP-2 :

La première amélioration du modèle FHP original, ensuite renommé FHP-1, fut d'ajouter une "particule immobile".

Cet ajout permet de porter le nombre de configurations à 128 et de rajouter de nombreuses opportunités inespérées

pour réarranger les particules en sorties. La viscosité chute et le modèle devient plus efficace. On commence aussi

à s'intéresser aux propriétés de dualité du modèle : dans le cas du choc frontal, remplacer une particule

par un "trou" et vice versa est tout à fait valable.

Les règles de collision additionnelles du modèle FHP-2.

La viscosité diminue et le nombre de collisions augmente : 20 entrées

mais l'occupation du champ de collision reste faible : 15 %.

Bien que les possibilités augmentent et que la définition du modèle FHP-2

ne soit pas très précise, il reste encore des efforts à faire.

II.9 : Caractéristiques particulières du modèle FHP-3 :

Le modèle sur lequel nous allons nous attarder est le modèle FHP-3. Il est une extension

du modèle FHP-2 avec une jeu de collisions saturé : 76 combinaisons sur 128 donnent

lieu à un réarrangement des particules à la sortie. 59 % : c'est le maximum d'occupation

du champ de collisions que l'on puisse obtenir avec 7 bits.

La table des collisions sera analysée en détail dans la partie IV

alors attardons-nous ici sur les raisons d'étudier ce modèle particulier.

Tout d'abord, ce modèle offre un compromis acceptable de simplicité et d'efficacité.

Il n'est pas plus avantageux de faire plus simple : les deux modèles

FHP décrits précédemment sont conceptuellement plus simples mais la surcharge en calcul

dûe aux collisions plus complexes de FHP-3 est largement compensée par la réduction du nombre de données

à traiter, donc le temps de calcul est réduit. Nous verrons aussi que les modèles FHP sont

memory bound sur la plateforme qui nous concerne, une accélération des calculs n'a

donc pas d'influence radicale sur le temps total de calcul car la mémoire est trop lente.

La programmation de FHP-3 est plus avantageuse que FHP-1 ou FHP-2 malgré une plus grande complexité.

Il n'est pas non plus envisageable à notre niveau de programmer un modèle plus efficace :

après FHP3, aucun modèle ne fait autorité et n'est suffisamment connu pour être utilisé

dans le cadre de notre étude de cas. Après FHP-3, le foisonnement d'améliorations a dispersé

les efforts et aucun nouveau modèle discret n'est assez maitrisée par le public novice. De plus,

la plus grande partie des nouveaux modèles implique une réorganisation complète des données et du programme :

nouveaux réseaux, nouvelles géométries, nouvelles lois et nouveaux artefacts à maitriser.

Enfin, notre travail doit rester une étude de cas simple et notre but n'est pas d'étudier

un nouveau modèle en profondeur : nous voulons simplement en faire fonctionner un le plus vite

possible.

FHP-3 est donc l'un des derniers modèles "stables" et connus avant la diversification

des modèles. On peut ainsi espérer que des techniques développées pour FHP-3 sont réutilisables

facilement dans les autres modèles. Ces techniques (notamment le strip mining)

et leurs implications seront ainsi facilement comprises par les utilisateurs qui les réutiliseront

et les amélioreront selon les cas.

II.10 : Propriétés physiques des modèles FHP :

Pour illustrer les propos du chapitre précédent, nous étudierons le tabelau suivant :

| modèle

| FHP-1

| FHP-2

| FHP-3

|

Cs

(vitesse du son en site par cycle)

|

|

|

|

| g

|

|

|

|

f*

(densité idéale, en occupation du site)

| 0,187

| 0,179

| 0,285

|

Re*

(Nombre maximal de Reynolds par site à la densité idéale)

| 0,387

| 1,08

| 2,22

|

Pour fonctionner correctement, à un nombre de Reynolds maximum, les Gaz sur Réseaux doivent être utilisés autour

d'une densité particulière qui dépend du modèle. Pour FHP-3, cette densité est heureusement simple : deux particules

par site (2/7 = 0,285). Si l'invariance galiléenne est nécessaire, la densité peut être différente.

La vitesse des écoulements doit aussi être limitée, en pratique à Mach 0.3 soit au maximum 0,6*0,3 = 0,2 sites

par pas de temps.

Puisque nous parlons ici du nombre de Reynolds, attardons-nous dans ce paragraphe sur sa définition. Pour simplifier

un peu arbitrairement, il met en relation la taille d'un objet ou d'un phénomène avec la viscosité du fluide.

Pour un gaz sur réseau, la viscosité correspond à une sorte de résistance à la diffusion d'une force ou d'une

perturbation dans toutes les directions. Ainsi, plus le nombre de Reynolds est élevé, plus les phénomènes se diffusent

et les géométries sont complexes.

Il est ainsi possible de comparer des phénomènes qui ont lieu à des vitesses différentes, à des échelles différentes,

à des pressions différentes dans des matières différentes, la complexité du phénomène est ainsi réduite à un seul

nombre sans unité. Il correspond aux équivalences suivantes, de la plus théorique à la plus pratique pour nous :

| avec |

|

En conséquence, avec un gaz sur réseau, nous pouvons déduire le nombre de Reynolds caractéristique

d'un écoulement à partir de la vitesse (en nombre de Mach) du fluide, multipliée par la longueur caractéristique de

l'écoulement (L) et l'efficacité du modèle (Re*).

Le tableau montre que le gain en efficacité en nombre de Reynolds entre FHP-1 et FHP-3 est environ d'un facteur 6.

Il faut donc en théorie 36 fois moins de sites et 6^3=216 fois moins de temps de calcul avec FHP-3 (puisque le temps

de calcul croît environ à la puissance troisième de la longueur caractéristique). Les paramètres idéaux d'utilisation

changent aussi, tout comme les caractéristiques (par exemple la vitesse du son). Le respect de ces paramètres

est crucial pour utiliser FHP de manière optimale et sans surprise : il suffit d'un écart pour observer

des phénomènes non physiques (artifacts).

De plus, on ne reviendra jamais assez sur l'importance de l'adimensionnement

lié à l'invariance galiléenne ! A densité idéale, la vitesse du fluide doit être multiplitée par 3/10

(voir la formule du tableau avec une densité de 2/7).

Pour les Gaz sur Réseaux du type FHP, d'autres phénomènes curieux, inattendus et inquiétants apparaissent. Pour des

écoulements à pression constante, les régions à plus grande vitesse ont une plus grande densité :

| avec |  |

| ce qui ne correspond pas à la formule normale : |  |

L'équation de Navier-Stokes pour le cas général est celle-ci :

Mais pour un Gaz sur Réseau (hexagonal) à basse pression et à basse vitesse, elle devient :

Le terme g(rho) est ajouté pour corriger l'invariance galiléenne. Il est donné dans le tableau précédent, où il dépend

de la densité. Selon les cas, il peut être intégré dans l'adimensionnement d'une grandeur (vitesse, pression, temps...).

Il faut alors choisir la densité en fonction du critère d'expérimentation, soit un grand nombre de Reynolds

ou l'invariance galiléenne, restaurée d'une manière ou d'une autre. La pression, la densité, la vitesse, la viscosité

et le temps sont ainsi enchevêtrés de manière complexe et leur étude sort du cadre de ce mémoire

puisqu'elle est disponible dans la littérature spécialisée. L'utilisateur est mis en garde du fait que la validité

des résultats dépend de la qualité de l'analyse du problème et de la compréhension intime des mécanismes mis en jeu.

Le programme seul ne pourra donner de résultat correct que dans des conditions contrôlées par l'utilisateur.

Les gaz sur réseaux FHP ne sont pas parfaits, nous le savons maintenant. Mais il y a surtout un détail

à rendre insomniaque car aucune solution simple n'est satisfaisante. Le problème peut être énoncé

de cette manière : si deux particules voyagent sur le même lien en sens inverse, elles ont moins d'une chance

sur deux pour être déviées dans un choc frontal. En conséqunce, la viscosité de FHP-3 est inférieure

à ce que le modèle pourrait fournir dans un cas idéal où tout événement d'une particule croisant une autre

donnerait lieu à une réorganisation des configurations. Le problème touche la nature même du réseau car un lien entre

deux noeuds a deux canaux unidirectionnels et indépendants. Il n'est pas possible de diviser

ce canal en deux tronçons et de tester les collisions à cet endroit car il faudrait disposer d'une autre

dimension ou direction pour réordonner les configurations à chaque temps t+1/2.

Le problème a été abandonné, les caractéristiques des réseaux existants étant estimés suffisamment satisfaisantes.

Mais surtout, il faut respecter le principe d'exclusion de Fermi qui stipule que deux particules ne peuvent pas

avoir la même position et la même vitesse au même instant.

Le dernier défaut reproché aux LGA booléens est la quantisation et le fort niveau de bruit. Il faut effectuer des

moyennes, ce qui empêche quasiment toute mesure ponctuelle. Un physicien préfère souvent 10% d'erreur à 10% de bruit

lorsqu'il veut effectuer un calcul.

Notons toutefois pour terminer que la précision d'un gaz sur réseau approche 1% dans des conditions idéales, soit

environ la précision de la mesure. Les méthodes traditionnelles sont qualitativement et quantitativement plus

imprécises en pratique et nécessitent de nombreuses mises à l'échelle ainsi que des mesures réelles.

II.11 : Extensions diverses :

Pour clore cette partie, nous allons voir quelques variations sur le thème des Gaz sur Réseaux. La première famille

conserve l'aspect binaire, ou dicret, de HPP/FHP : des modèles thermiques, comme évoqués précédemment,

ont été étudiés (géométrie D2Q9) [13]. Diverses études ont permis de mieux contrôler

l'invariance galiléenne du modèle : par exemple le modèle FHP-4 avec plusieurs particules immobiles

[20][28][29]. Des modèles à plusieurs

phases (matières) miscibles ou immiscibles permettent d'injecter des "traceurs" dans des écoulements, ou de

simuler la séparation de deux fluides (comme de l'huile se séparant de l'eau)

[9][15][16]. En 1988,

Jean-Pierre Rivet [11] programme un Gaz sur Réseau en 3D à grande échelle sur un réseau FCHC

(HyperCube à Faces Centrées). En 1990, C. Appert et S. Zaleski ajoutent des forces non locales entre

particules pour calculer la séparation de phases.

Les LGA discrets ont vite été supplantés par la famille des LGA en virgule flottante car leur rapport efficacité/temps

de calcul est plus intéressant. La disponibilité de plateformes suffisamment puissantes a permis à ce domaine

de croître au point de canaliser la plupart des efforts de recherche. Les utilisateurs de CAM-8 sont probablement

les derniers à utiliser des modèles discrets. La première raison d'utiliser les nouveaux modèles est simple :

il n'y a pas besoin d'intégrer de nombreux points pour effectuer une mesure. Les modèles discrets sont intrinsèquement

bruités et les physiciens détestent le bruit. Ce bruit est pourtant intéressant pour faire émerger des phénomènes

spontanément alors qu'ils sont forcés dans la pratique (par exemple : dissymétrie dans un tunnel pour forcer

des allées de Von Karman à apparaitre rapidement, voir la partie III.9).

Pour réduire la viscosité, les nombres en virgule flottante sont utilisés car ils ont une plage dynamique bien supérieure

à un seul bit. Toutefois on ne peut plus utiliser les techniques de collision classiques ! On utilise alors les méthodes

de Bolzman, l'opérateur BGK est le plus souvent utilisé actuellement. Le nombre de Reynolds est bien plus grand

et les mesures sont plus faciles avec un même nombre de sites, même si ces sites prennent plus de place en mémoire

qu'un site FHP. La méthode de Bolzman est utilisée dans presque tous les domaines actuellement, avec autant

ou plus de diversité que le modèle FHP, même si le débogage est encore plus difficile qu'avec FHP :

lorsque la densité n'est pas exactement conservée, on ne peut pas savoir exactement si c'est une erreur

d'arrondi, de frappe ou de formule...

Enfin, puisque le bruit est nécessaire dans certains cas, Boghossian et al. [35]

ont introduit les ILG : Integer Lattice Gases, sensés avoir à la fois les avantages des modèles discrets

et continus. Les premières expériences ont calmé l'optimisme initial, mais tout espoir n'est pas perdu.

II.12 : Conclusion :

Le modèle FHP-3 allie une simplicité relative à des caractéristiques suffisamment intéressantes pour justifier

les efforts de programmation qui sont effectués dans ce domaine. Nous avons toutefois constaté qu'il ne peut

être utilisé que dans un nombre restreint de cas et dans des conditions sévèrement contrôlées mais notre étude porte

uniquement sur les aspects architecturaux et algorithmiques de ce type de modèles. Cette deuxième partie est la seule

qui porte sur les aspects purement théoriques et nous pouvons maintenant nous intéresser aux algorithmes dans tout

le reste de ce mémoire, tout en étant conscient des possibilités et des limites du modèle.

Partie III : Présentation des travaux antérieurs

III.1 : Introduction :

Après la partie précédente, qui rappelle les points clés de mécanique qui nous concernent, cette partie

présente les techniques classiques et basiques pour programmer les Gaz sur Réseaux.

Elle est la base et le point de départ du travail réalisé pour ce mémoire.

La première implémentation de référence est donnée en annexe B : elle a fait l'objet d'un article

dans le journal Pascalissime et permet de comprendre les problèmes de base posés par le modèle FHP3.

Nous étudierons la structure et la conception du programme puis les problèmes rencontrés pour arriver à

la description d'une deuxième implémentation de référence plus sophistiquée. Enfin nous analyserons plus

en profondeur les caractéristiques de la programmation des LGA pour préparer la version de ce mémoire.

III.2 : Idées de base :

Le premier programme, écrit à l'origine en Turbo Pascal, a été inspiré par l'article de

Pierre Lallemand, paru Revue du Palais de la Découverte [18] et décrivant

approximativement le modèle FHP-2. Le seul paragraphe dans lequel la programmation est abordée est celui-ci :

"

Nous donnons d'abord quelques brèves indications sur ces expériences, pour susciter d'éventuelles vocations

auprès des lecteurs disposant d'un ordinateur personnel. Chaque noeud du réseau est représenté par un nombre

formé par la juxtaposition de sept nombres égaux à 0 ou 1 (bits) : un octet de la mémoire d'ordinateur suffira

donc pour décrire chaque site. L'évolution temporelle se fait en deux étapes :

propagation des particules par déplacement vers les noeuds voisins des bits convenables

collision en chaque noeud en allant lire dans une table préparée une fois pour toutes le résultat de la collision

particulière.

"

Mais ces indications m'ont longtemps laissé perplexe. J'ai ensuite cherché de l'aide dans les thèses de Valérie Pot

[15] et d'Umberto d'Ortona [14] à Jussieu mais aucun code

et aucune indication ne sont fournis. Pourtant, les questions suivantes sont simples :

- Que contient la table, et comment la fabrique-t-on ?

- Que représentent les bits ? Un lien ou un noeud ?

La première question est résolue par du "travail sur papier" et une analyse exhaustive des collisions possibles.

Le travail est effectué avec des représentations vectorielles des configurations afin de trouver des réorganisations

possibles. Pourtant, les efforts seuls, sans source de référence, ont donné la table des collisions de

l'annexe B

qui n'est pas complétement juste, malgré un bon début. Les progrès sont difficiles sans exemple, ce qui motive en retour

l'aspect instructif de ce mémoire. Nous reviendrons sur la constitution de la lookup table dans la partie IV.

La représentation des données est un problème tout aussi compliqué lorqu'aucune référence n'est disponible. En effet,

même s'il est clair qu'un bit peut représenter une particule et qu'un octet permet de représenter toutes les

directions, un pas de temps comporte de nombreux pas intermédiaires et le réseau représente l'état figé des particules

à un instant qui n'est pas précisé par le modèle. En effet, un pas de temps commence-t-il par une collision

ou un déplacement ? Représentons-nous les particules qui entrent ou qui sortent ? Un bit représente-t-il un lien

ou un noeud ? Comment organiser les données pour qu'elles soient facilement manipulées ?

Une fois que la transposition d'un réseau carré à un réseau hexagonal est comprise, nous pouvons partir d'un

"ether" simple et bâtir l'algorithme de calcul à partir du code de déplacement.

Tout d'abord, le calcul est effectué cycle après cycle, et l'état

du réseau représente les particules à chaque cycle, sans se préoccuper de la sous-étape (avant ou après collision

ou déplacement). Ce qui importe est le changement entre chaque cycle : une particule se propage cycle après cycle

en sautant d'un noeud à un autre. Pour effectuer ce changement, la fonction de "calcul" effectue les deux opérations

(propagation et collision), une cellule après l'autre. Effectuer les deux opérations l'une après l'autre

sur tout le réseau impliquerait la programmation de deux boucles indépendantes et augmenterait le nombre d'accès à

la mémoire. Dans tous les algorithmes qui suivront, les deux opérations sont effectuées à l'intérieur de la même boucle

pour bénéficier de la localité des registres.

La technique d'élaboration du programme est simple :

- D'abord mettre en place la boucle externe avec la préparation des pointeurs vers les données.

- Ensuite, programmer la propagation des particules : charger un octet de mémoire et distribuer

un par un tous les bits vers les noeuds voisins, avec la gestion des variables temporaires (pour éviter le

recouvrement dans certaines directions, comme expliqué dans le chapitre suivant).

- Enfin, lorsque le déplacement est fonctionnel (tous les bits se déplacent comme prévu sur le réseau),

il ne reste plus qu'à inclure la consultation de la table, juste après l'endroit où le noeud courant est lu.

Il devient clair aussi que la table, puisqu'elle est consultée entre le chargement et la distribution, doit contenir

une représentation aussi simple et complète que possible des opérations à effectuer. La table peut effectuer des

opérations complexes et réduire la taille du programme, elle concentre donc toute l'intelligence du code de collision.

L'annexe B montre deux manières de la programmer : par code explicite ou par constante à la compilation. La table

exploite ainsi le huitième bit pour effectuer la collision avec des "murs" virtuels sans ajouter une seule ligne de

code. Des effets de pesanteur ou d'attraction peuvent même être ajoutés en modifiant légèrement certaines

entrées de la table. C'en est presque trop facile ...

III.3 : Les plans temporaires :

Un aspect méconnu des programmes de ce type concerne les "plans temporaires" : le problème ne peut être appréhendé

dans toute sa complexité que lors de la programmation, lorsqu'il est déjà trop tard. Ce problème deviendra

encore plus prépondérant avec les codes de strip mining et il est important pour la suite du travail de maitriser

parfaitement l'algorithme et les données associées.

Les "plans temporaires" deviennent très important pour les géométries très larges car même avec un ordinateur

disposant de toute la mémoire vive du monde, il est important de l'utiliser correctement. Les plans temporaires

sont décris succintement dans l'annexe B et dans la partie V.6 mais étudions ici

leur théorie générale en partant d'un cas de dimension 1 (par exemple un automate cellulaire linéaire) :

Dans un ordinateur "séquenciel", les noeuds sont traités un par un. Supposons que le sens de balayage soit

le même que le sens de x et regardons ce que ferait un algorithme simple mais mauvais :

1) d'abord il lit la valeur du noeud courant en x,

2) ensuite il calcule la valeur suivante,

par consultation de la table par exemple,

3) enfin il écrit une partie du résultat dans chaque

partie correspondante : x-1, x et x+1

4) il incrémente x et retourne en 1) si la ligne n'est pas terminée. |

Cet algorithme est mauvais car au cycle suivant de la boucle du temps t, il trouvera en x+1

une valeur qui correspondra à t+1 et la catastrophe sera inévitable :

La solution la plus simple est d'utiliser deux plans de travail : un plan "source" et un plan "destination", permettant

une complexité arbitraire dans le voisinage avec l'argument choc que le "transfert" s'effectue simplement en échangeant

les deux pointeurs vers les tableaux :

Toutefois, lorsque la taille totale des tableaux atteint les limites de la mémoire de l'ordinateur, il est clair

que seule une moitié est vraiment utile car les informations sont redondantes ou inutilisées. Cette considération

devient incontournable pour les simulations en 3D car elles utilisent une quantité phénoménale de mémoire

(de 16MO à 4GO dans certains cas). L'argument de simplicité de la technique

de l'échange de pointeurs perd toute crédibilité devant ce problème.

La solution privilégiée, bien que plus complexe, utilise un "plan temporaire" pour mémoriser le résultat de chaque cycle

et éviter le "court circuit temporel" décrit plus haut. Les caractéristiques de cette mémoire dépendent de la quantité

d'informations qui doit voyager dans le même sens que celui du balayage. Pour l'exemple de l'automate cellulaire

linéaire décrit plus haut, il faut mémoriser un mot ou un bit car le déplacement se fait vers le voisin immédiat.

Au niveau de l'algorithme, cela se traduit par la nécessité de retarder l'écriture du résultat. Le programme

est doté d'une valeur temporaire (plan ponctuel) et devient ainsi :

1) lire la valeur du noeud courant en x,

2) écrire en x la valeur temporaire,

3) calculer la valeur suivante de x,

4) écrire chaque partie du résultat dans chaque partie correspondante :

x-1, x mais x+1 va dans la valeur temporaire.

5) incrémenter x et retourner en 1) si la ligne n'est pas terminée. |

Le graphe de dataflow suivant illustre une autre manière de résoudre le problème :

Une difficulté supplémentaire est d'amorcer le programme en fournissant une valeur initiale correspondant

à l'extrémité de la ligne : cela peut être astucieusement utilisé pour injecter des particules dans le

domaine d'étude et créer un vent artificiel. De même, la valeur finale de la variable temporaire (à la fin de la

ligne) peut être ignorée pour faire disparaitre les particules et créer une sorte de bouche de sortie

pour le fluide. Les particules peuvent ainsi être créées puis effacées à des extrémités opposées du tunnel,

ce qui génère naturellement un vent dans le tunnel. Des techniques plus sophistiquées sont cependant

recommandées car cette méthode est aussi simple que limitée dans la pratique.

Toutefois nous traitons des tableaux en deux dimensions et les choses ont tendance à s'emmêler et rendre la programmation

très délicate. Il y a pourtant une règle simple à retenir : il faut un buffer temporaire par dimension

(que la dimension soit temporelle ou spatiale) et l'information à mémoriser correspond au voyage qu'effectuent

les particules dans le sens du balayage.

Pour appliquer l'algorithme en 2 dimensions, il faut un plan temporaire indépendant pour chaque

dimension. Les colonnes sont traitées exactement de la même manière qu'une ligne

mais après projection sur la dimension perpendiculaire : ce n'est plus un noeud de mémoire

qui est nécessaire pour le plan temporaire mais toute une ligne. Pour un tableau de x * y noeuds, il faudra en tout

M = 1 + x + xy noeuds en mémoire.

En règle générale, on compte (x+1)*y noeuds pour l'allocation de la mémoire d'un tableau 2D.

La formule se généralise facilement à toute dimension N>1 et elle se réduit approximativement

à la un polynôme si toutes les dimensions sont similaires. On peut ainsi

prouver que la quantité totale de mémoire ne s'approche pas du double de la taille du tunnel comme

dans l'alternative précédente.

Par exemple, pour un réseau en 3D de dimensions (x,y,z) avec un voyage d'un noeud par pas de temps, il faudra

en tout M = 1 + x + xy + xyz noeuds de mémoire. Si x, y et z

sont des valeur rapprochées, la formule devient le polynôme suivant :

M = x^0 + x^1 + x^2 + x^3 = 1 + x + x^2 + x^3.

Elle tend ainsi vers M = (x+1)^N et permet, pour un cas donné,

d'utiliser moins de mémoire ou d'avoir un tableau plus grand, par rapport à la technique de l'échange de pointeurs

(M = 2x^N).

Naturellement, la complexité du programme augmente mais comme pour le reste cela dépend de l'expérience,

des ressources, de la patience et de la compréhension de la technique. Un cas intermédiaire (compromis

complexité/espace mémoire) serait de diviser le tunnel en de nombreuses parties et de disposer d'un plan

temporaire : chaque bloc ayant la même taille, il est facile d'utiliser la technique d'échange de pointeurs

sans pour autant doubler l'occupation de la mémoire. Cette technique ne permettant pas de réduire

directement le temps de calcul, elle n'est pas étudiée ici. De plus, les fortes contraintes en mémoire sur les PC

ainsi que les mémoires caches (principalement les modes write through et write back qui ne peuvent

pas toujours être contrôlés) favorisent la technique de plan temporaire minimal, décrite plus haut.

III.4 : Premier code de référence :

Nous allons ici étudier succintement un premier morceau de code qui servira de référence pour estimer les

performances, les contraintes et les limites des algorithmes réalisés. Il est extrait de

l'annexe B et c'est la version écrite en assembleur pour i286 en 1995 :

BEGIN

(*...*)

asm

(*...*)

(* boucle principale *)

@BOUCLE_EXTERIEURE:

mov seg_ligne,$A000

mov y,99

@BOUCLE_Y:

mov es,seg_ligne

(* PARTIE IMPAIRE: *)

(* force la particule D *)

xor cl,cl

rol rand,1

jnc @pas_retenue1

mov cl,1

@pas_retenue1:

mov bp,1 (* BP est le registre de contrôle de la boucle *)

mov di,xmax+2 (* DI pointe sur le noeud courant *)

mov si,offset temp_impair+1 (* SI pointe sur les bits E et F *)

@BOUCLE_IMPAIRE:

(* Al collectera les bits du noeud courant *)

lodsb [1]

mov byte[si-1],0 [2]

(* Ah désignera les bits à envoyer *)

mov ah,byte ptr es:[di] [3]

or ah,ah [4]

jz @vide1 [5]

(* consulte le tableau: *)

mov bl,ah [6]

xor bh,bh [7]

rol rand,1 [8]

jnc @pas_rol1 [9]

inc bh [10]

@pas_rol1:

mov ah,byte[bx+offset p] [11]

(* distribue les bits: *)

shr ah,1 [12]

jnc @pas_A1 [13]

or byte ptr es:[di-1],A [14]

@pas_A1:

shr ah,1 [15]

jnc @pas_B1 [16]

or byte ptr es:[di-xmax-1],B [17]

@pas_B1:

shr ah,1 [18]

jnc @pas_C1 [19]

or byte ptr es:[di-xmax],C [20]

@pas_C1:

shr ah,1 [21]

jnc @pas_D1 [22]

or cl,2 [23]

@pas_D1:

shr ah,1 [24]

jnc @pas_E1 [25]

or byte ptr ds:[bp+offset temp_pair],E [26]

@pas_E1:

shr ah,1 [27]

jnc @pas_F1 [28]

or byte ptr ds:[bp+offset temp_pair-1],F [29]

@pas_F1:

shl ah,6 [30]

or al,ah [31]

@vide1:

shr cl,1 [32]

jnc @pas_retenue_D1 [33]

or al,8 [34]

@pas_retenue_D1:

stosb [35]

inc bp [36]

cmp bp,xmax [37]

jbe @BOUCLE_IMPAIRE [38]

(* PARTIE PAIRE: *)

(* coupée : elle est similaire à la partie impaire *)

add seg_ligne,40

dec y

jnz @BOUCLE_Y

mov ah,1

int 016h

jz @BOUCLE_EXTERIEURE

end;

(* boucle principale *)

END. |

or byte ptr ds:[bp+offset temp_pair],E : nous atteignons ici des sommets

de programmation CISC. Rappel : le nombre réduit de registres nous oblige à

utiliser comme compteur/pointeur le pointeur de trame BP (frame Base Pointer),

alors qu'il est sensé servir pour le passage de paramètres sur la pile pour les langages

de haut niveau. Le problème est que tout adressage

utilisant BP utilise par défaut le segment de pile SS alors que les données sont adressées

par ES (le tableau dans la mémoire vidéo) et DS (les données statiques

et le plan temporaire). Nous devons donc ajouter un préfixe d'adressage ("DS:")

pour restaurer le segment, ce qui consomme inutilement des cycles.

Rappelons aussi que sur le i286, bien qu'il existe de nombreux

modes d'adressage, peu de registres peuvent être effectivement utilisés comme pointeur. Il

est donc facile de comprendre que c'est l'architecture bancale de la machine qui fait dire

à certains que "les compilateurs peuvent générer du code aussi efficace qu'un code

écrit en assembleur", puisque la flexibilité réduite diminue artificiellement les écarts

possibles de performance.

Nous voyons aussi, dans le reste du code, de nombreuses boucles, des manipulations de segments,

des calculs de pointeurs et la gestion du plan temporaire horizontal : de nombreuses

parties du programme seraient susceptibles d'être éliminées en retravaillant la structure

globale. Bien que le programme en assembleur

soit environ deux fois plus rapide que le programme en Pascal, il semble effectuer des opérations

trop complexes pour ne bouger que quelques bits. Il faut environ 38 instructions pour traiter une

seule cellule et le traitement est ralenti pour de nombreuses raisons, dont :

- l'accès aux instructions qui ne sont pas "cachées" et utilisent une partie

de la bande passante de la mémoire (le problème n'existe plus depuis le i486)

- les accès aux données en mémoire vidéo qui entrent en concurrence avec le balayage de la carte

- les nombreux sauts en avant de quelques octets qui réduisent l'efficacité de la

queue de prédécodage interne

Rappelons aussi qu'un PC à base de i286 n'a pas de mémoire cache et tous les accès à la mémoire

centrale nécessitent d'envoyer une adresse à des puces de DRAM dont le temps d'accès est environ

de 70 ns. Malgré l'apparition de chipsets sophistiqués et le début des optimisations

matérielles, les instructions du coeur de la boucle consomment de la bande passante, ce qui

entre en concurrence avec les autres accès à la mémoire. Le programme est naturellement

memory bound à cause de l'architecture du processeur.

Les mesures manuelles sur un PC i286 à 12MHz donnent une vitesse d'environ 100000 noeuds par

seconde, la géométrie étant limitée architecturalement à 320*200 par la mémoire segmentée et

la carte VGA (granularité de 64 Ko). Il y a environ une image et demie affichée par seconde

ce qui est honnorable pour un ordinateur de cette classe (comparer à l'iPSC en

D.6). La recherche des goulots d'étranglements

est difficile car le processeur i286 exécute les instructions avec des durées très variables

et le temps d'accès à la mémoire est très fluctuant. Toutefois nous pouvons effectuer quelques

estimations : le calcul d'un noeud nécessite environ 120 cycles d'horloge et 38 instructions,

soit 3,2 cycles d'horloge par instruction en moyenne.

III.5 : Influence de l'architecture :

Le passage du i286 à 12MHz au Pentium à 100MHz en 1996 fut un grand bouleversement.

Les règles de codage ont été profondément modifiées : les instructions recommandées

ne sont pas les mêmes, la mémoire cache sur deux niveaux peut enfin contenir tout le code

et toutes les données (L1 : 8Ko et L2 : 256Ko), de nombreuses innovations sont incluses...

Pourtant le mode réel ne bénéficie pas directement de toutes les améliorations, comme

par exemple les modes d'adressage étendus et orthogonaux du i386 qui permettent d'utiliser

toutes les combinaisons de registres pour accéder à la mémoire.

La mémoire virtuelle en mode protégé reste un problème car la manipulation des

registres de segments déclenche de longues séquences de microcode pour vérifier la validité des

adresses, ce qui en plus peut déclencher des exceptions pour gérer les pages en mémoire et

sur le disque dur s'il faut les swapper. On s'attend donc naturellement à ce que le programme

fonctionne moins vite lorsqu'il est lancé à partir de Windows. Pourtant, il s'y exécute visiblement

plus vite ! Plus précisément, en mode fenêtré, il s'exécute beaucoup plus vite qu'en mode

normal/"plein écran".

Le changement d'architecture, du 286 au Pentium, a changé complétement les rapports entre les

flux de données et d'instructions. L'introduction de deux niveaux de mémoire cache balance

la plus grande latence relative de la mémoire vidéo. De plus, l'accès à la mémoire vidéo subit de

nombreuses restrictions : par exemple, elle est accédée au travers du bus PCI et elle n'est pas

cachable. L'expérience avec Windows a montré la situation paradoxale où un programme "optimal" pour le

286 est inefficace sur Pentium. Pour expliquer cela, il faut préciser que Windows (en mode fenêtré)

émule la mémoire vidéo : il redirige les accès vidéo vers la DRAM centrale grâce

à la translation d'adresse du mode protégé/paginé. Ainsi, nous n'accédons pas nous-mêmes

à la mémoire vidéo, c'est l'émulateur qui copie la DRAM périodiquement vers la vraie carte.

La mémoire centrale étant cachable, les accès sont beaucoup plus rapides et le

transfert par bloc vers l'écran est plus rapide qu'octet par octet. Les instructions de type

read-modify-write sont encore plus lourdes puisqu'elles nécessitent

une lecture (blocante, pour éviter toute modification intempestive au milieu de l'instruction)

puis une écriture et il faut une transaction complète sur

le bus PCI (attente que le bus soit libre - envoyer l'adresse - envoyer/recevoir la donnée)

pour transférer un simple octet ou un bloc entier.

Le calcul en mémoire cachable puis le transfert par bloc (ou en rafale, burst pour le PCI)

est forcément plus rapide que le premier programme.

Le diagramme ci-contre est extrait de [33]. Il représente une

carte mère aux caractéristiques suivantes :

* Processeur Pentium 100MHz avec 2 caches intégrées de 8Ko chacune

* Bus local : données 64 bits, 66 MHz, 528Mo/s théoriques

* Cache L2 de 256Ko avec des puces SRAM à 15 ns de temps d'accès (sans compter

les latences de gestion de la LRU et de la SRAM de "tag" à 15 ns aussi)

* Mémoire DRAM à 70ns de temps d'accès (30ns en mode page), EDO possible.

* Bus PCI multiplexé à 33MHz et 32 bits de large (132Mo/s théoriques)

|  |

Nous pouvons y voir que le nombre de circuits et de connexions à traverser

est proportionnel à la latence et à la vitesse de transfert. Le circuit imprimé

montre en plus que cela est proportionnel à la distance parcourue dans les fils :

la mémoire cache est très proche du processeur alors que les slots PCI et DRAM

sont éloignés.

Des mesures réelles sur cette plateforme, en conditions "idéales", donnent une

vitesse de transfert unidirectionnel de 28Mo/s vers la carte vidéo. En pratique,

le processeur peut donc afficher un mot de 32 bits tous les 4 cycles, soit une

instruction d'affichage entrelacée avec sept instructions de calcul. Il n'est pas

raisonnable dans ces conditions d'utiliser le premier code de référence qui utilise

de nombreuses opérations complexes vers la mémoire vidéo.

La leçon est simple : en mode "normal" (MS-DOS) il ne faut plus utiliser la mémoire vidéo pour

stocker le tunnel. Il faut au contraire utiliser une méthode qui paradoxalement prendrait plus

de temps si l'on ne regardait que le nombre d'instructions à exécuter. Le calcul doit donc

s'effectuer dans la mémoire centrale et, comme l'émulateur MSDOS de Windows le faisait,

afficher régulièrement le résultat à l'écran, tous les N pas de temps (N pouvant varier

à la demande de l'utilisateur). Nous évitons ainsi de perdre du temps dans les transactions

"blocantes" du bus PCI, dont le temps d'accès est probablement supérieur à 100ns (carte vidéo

comprise). Pour qu'un programme tourne vite, il est crucial de placer les données au meilleur

endroit.

III.6 : Deuxième code de référence :

Le second code de référence date de 1997 et est inclus ci-dessous. L'idée directrice est de réduire

le code de distribution des bits en groupant les noeuds par quatre. Le réseau est alors

tourné à 90 degrés et il n'y a plus de code pour les lignes paires et impaires, comme pour le circuit

décrit en V.6. Ce code est destiné aux plateformes à partir du i386 et "optimisé"

pour le Pentium classique (P53C) où nous pouvons utiliser les registres sur 32 bits au lieu de 16.

La boucle externe affiche les calculs puis traite N pas de temps de cette manière :

;

; BALAYAGE:

;

mov ebx,es:[640]

mov XB,ebx

mov di,640

boucle_ext:

mov bx,320

boucle_int:

mov word ptr X,bx ;U (1)

;

; déplacement des variables:

;

mov esi,XC ;*V [3]

mov ebx,es:[di-316] ;*prefixe + U (3) [6]

mov XD,esi ;*V [8]

mov XC,ebx ;*U (4) [10]

mov edx,X1 ;*V [12]

mov eax,XB ;*U (5) [14]

mov ecx,es:[di+4] ;*préfixe+U (7) [17]

and edx,010000000h ;XE ;*V [19]

mov X1,eax ;*U (8) [21]

mov XB,ecx ;*V [23]

mov ebp,XA ;*U (9) [25]

mov ebx,es:[di+320] ;*préfixe+U (11) [28]

and ebp,020000000h ;XF ;*V [30]

mov XA,ebx ;*U (12) [32]

or ebp,edx ;*V [34]

;verticaux:

and eax,0C0C0C0C0h ;*U (13) [36]

and esi,008080808h ;*V [38]

and ebx,001010101h ;*U (14) [40]

or eax,esi ;*V [42]

;XL

mov ecx,XD ;*U (15) [44]

or eax,ebx ;report des verticaux *V [46]

mov ebx,XA ;*U (16) [48]

and ecx,000100010h ;*V [50]

and ebx,000002000h ;*U (17) [52]

or ebp,ecx ;*V [54]

mov ecx,X1 ;*U (18) [56]

or ebp,ebx ;*V [58]

and ecx,000201020h ;*U (19) [60]

or ebp,ecx ;*U (20) (dépendance sur ECX) [62]

;XR:

mov ebx,XB ;*V [64]

rol ebp,8 ; report XL *U (21) [66]

mov ecx,XC ;*V [68]

or eax,ebp ; report XL *U (22) [70]

mov ebp,XD ;*V [72]

and bx,2 ;U (23) [72']

and ebp,000040000h ;*V [74]

and cx,4 ;U (24) [74']

mov edx,XA ;*V [76]

or bx,cx ;U (25) [76']

mov ecx,X1 ;*V [78]

or bp,bx ;U (26) [78']

and edx,002000200h ;*V [80]

or ebp,edx ;*U (27) [82]

and ecx,004020400h ;*V [84]

or ebp,ecx ;*U (28) [86]

ror ebp,8 ;*V [88]

or eax,ebp ;*U (29) [90]

; détermine quelle banque LUT on utilise:

rol word ptr seed1,1 ;U (32) 3 cycles + non pairable [94]

setc bh ;U (35) microcode [97]

mov bl,ah ;U (36) dépendance sur EBX [98]

mov ah,[offset p+bx]

; accède au tableau (#1) U (38) AGI sur EBX, préfixe possible [101]

mov bl,al ;U (39) dépendance sur EAX [102]

mov al,[offset p+bx]

; accède au tableau (#2) U (41) AGI sur EBX, préfixe possible [105]

ror eax,16 ;U (42) dépendance sur EAX [106]

mov bl,ah ;U (43) dépendance sur EAX [107]

mov ah,[offset p+bx]

; accède au tableau (#3) U (45) AGI sur EBX, préfixe possible [110]

mov bl,al ;U (46) dépendance sur EAX [111]

mov al,[offset p+bx]

; accède au tableau (#4) U (48) AGI sur EBX, préfixe possible [114]

ror eax,16 ;U (49) dépendance sur EAX [115]

;writeback:

mov bx,word ptr X ;V [115']

mov ecx,[offset temp+bx] ;**U (50) [117]

mov [offset temp+bx],eax ;*V [119]

mov es:[di-320],ecx ;préfixe+*U (51) [122]

add di,4 ;V [123]

sub bx,4 ;U (52) [123']

jnz boucle_int ;V [124]

cmp di,63360

jbe boucle_ext |

La boucle interne comporte 67 instructions pour traiter 4 noeuds, soit environ 17 instructions par noeud :

c'est deux fois mieux que le code de référence en mode 8 bits.

Une estimation "statique", rapide et optimiste de ce kernel sur un Pentium classique fait penser qu'il peut

s'exécuter en 52 cycles (voir les nombres entre parenthèses, soit 13 cycles par noeud).

Mais en réalité, le code a été conçu pour être

exécuté en mode réel (16 bits sous MS-DOS) et l'utilisation des registres en mode 32 bits ajoute un préfixe de taille, invisible dans la syntaxe, à

chaque instruction : cela brise complétement le pairage des instructions !

La plupart des dépendances de données entre les registres ont été aplanies dans le code de mouvement afin

d'exécuter deux instructions par cycle sur le Pentium mais les préfixes de taille étaient oubliés dans l'analyse.

Les instructions marquées d'un astérisque prennent ainsi deux cycles au lieu d'un demi-cycle !

Cela montre bien que le nombre d'instruction, le temps d'exécution et le nombre de sites traités par seconde

sont des valeurs qui ne sont plus naturellement ou simplement proportionnelles : l'architecture complexe du Pentium

a des "cycles cachés" qui n'apparaissent pas en lisant le code source, même en assembleur ! Alors que ce code

est très bon pour le i386, le Pentium a un pipeline différent qui favorise certains types de codes

tout en pouvant exécuter les autres programmes mais à une vitesse nettement inférieure et sans prévenir.

L'analyse sous ce nouvel angle (voir les nombres entre crochets)

donne environ 124 cycles (comme pour la version i286, mais 31 cycles par noeud). Cette baisse incroyable

des performances, malgré le soin apporté au code, a motivé la conception d'un DOS-extender pour la suite du projet.

Le code de mouvement a été assez bien réduit mais reste lourd et consomme tous les registres.

L'analyse du code révèle aussi que le processeur effectue des opérations inutiles ou perd du temps à manipuler

des données entre les registres. Ainsi, la consultation des tables, en raison du faible nombre de registres disponibles,

du jeu d'instructions, des préfixes et des dépendances croisées, prend 20 cycles au moins, bien qu'en théorie cela

nécessite 4 cycles pour un cas "simple et idéal".

|

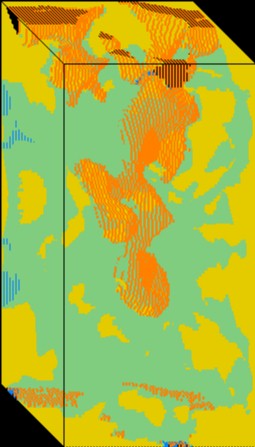

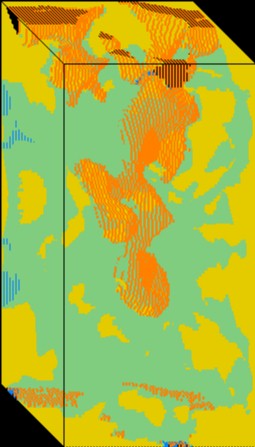

La densité globale dans le domaine d'étude peut être déterminée en accumulant le nombre de particules

à chaque pixel. Nous voyons ici une accumulation sur 8 bits avec deux dépassements (les mêmes couleurs sont utilisées

deux fois pour des densités différentes) et un écoulement de Poiseuille caractéristique. L'image peut être calculée

interactivement (les paramètres peuvent être changés) en une minute environ.

|  |

L'accumulation doit commencer après la stabilisation du fluide et la disparition des ondes de choc.

Il faut ici pouvoir gérer trois tableaux de 64 Ko, ce qui est à la limite des possibilités du

mode réel du x86. Avec un code de ce type, il a fallu deux heures à un Pentium à 100 MHz

pour calculer l'image suivante :

|

A chaque pas de temps, la densité de chaque noeud est accumulée sur 16 bits dont nous voyons ici les 8 bits de poids

fort. Il faut donc un tableau de 128Ko en mémoire et accéder en tout à plus de 200Ko, ce qui a nécessité

l'emploi du mode flat (ou unreal). Ce programme est donc difficilement transportable et nécessite

une configuration très précise pour fonctionner.

|

Le bruit au niveau de l'octet de poids fort est réduit mais il a fallu beaucoup de temps de calcul

pour que toute la dynamique de l'octet soit utilisée et donne une image utilisant toutes les couleurs

de la palette (plus de 64K*3=200000 pas de temps). La vitesse de rafraichissement pour ce type de

code sur cette machine atteint environ 10Hz et la taille est fixée à 320x200 noeuds, c'est à dire

la résolution de l'écran.

III.7 : Conditions aux limites et effets de bords :

Les LGA permettent de calculer les équations différentielles de Navier-Stokes dans

des conditions idéales de très faible vitesse et de taille infinie du réseau [19].

Toute autre condition ne permet d'effectuer qu'une approximation, par exemple lorsque la taille est finie

(limitée par la taille de la mémoire de l'ordinateur), ou alors

la simulation ne correspond pas aux réalités physiques. Entre autres exemples, la vitesse du fluide

ne doit pas dépasser Mach 0,3 environ mais en plus des limites théoriques, les limites pratiques

sont aussi difficiles à connaitre et à comprendre.

Nous allons étudier en particulier le cas d'une éprouvette dans une soufflerie ainsi que

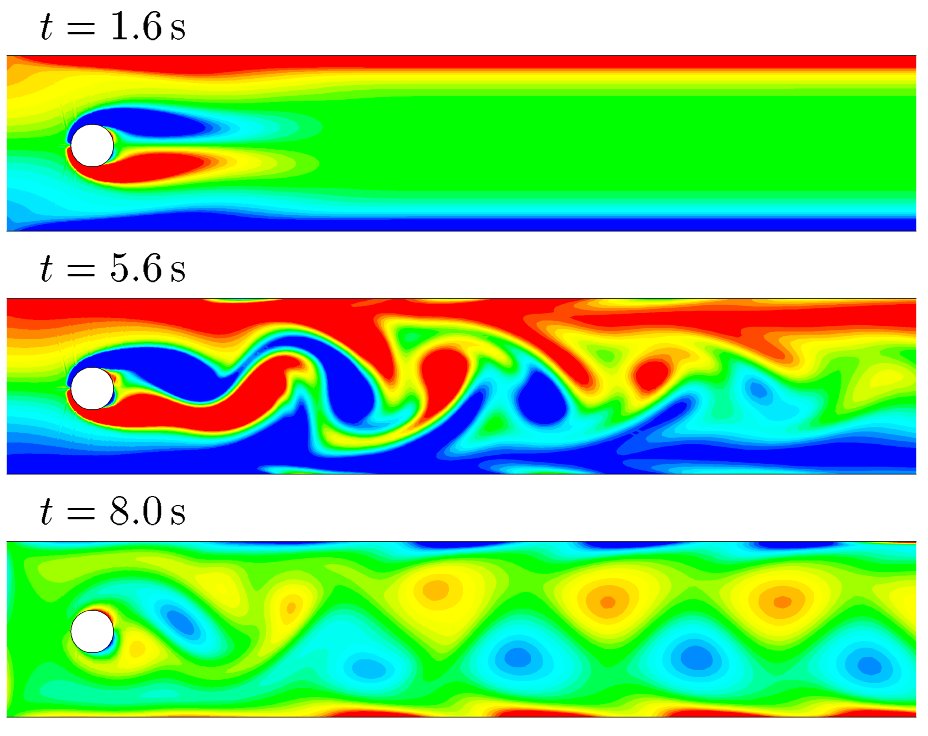

les effets de bords liés aux conditions aux limites.

Dans les images précédentes, nous pouvons observer certains phénomènes qui influencent la simulation

et ses résultats. Tout d'abord, avant chaque pas de temps, le vent est généré par une boucle

qui crée de nouvelles particules afin de générer un "vent" dans le tunnel. Les propriétés de ce flux ont

des conséquences directes sur le temps de disparition des phénomènes transitoires et indésirés.

La manière la plus simple, comme le permet l'algorithme de plan temporaire décrit précédemment,

est de créer une particule directement dans le sens du vent. Cela correspond bien à

la théorie mais dans la réalité, un vent n'est pas constitué de particules allant toutes

dans la même directions : ce serait un vent supersonique ! De plus, les phénomènes dépassant

Mach 0,4 ne sont pas fidèles à la réalité. Il faut donc créer un flux d'air,

non une masse homogène ou homocinétique irréelle. La vitesse et la direction des particules doivent être

bien choisies. La vitesse des particules ne peut pas être modifiée car elle est unitaire :

la vitesse du flux sera réglée par la "vitesse" d'introduction et de destruction des particules

de chaque côté du tunnel. Une autre méthode est de "forcer" certaines particules au hasard

dans le tunnel en changeant leur direction mais c'est plus compliqué car le tunnel devra être

bouclé sur lui-même comme un tore, ce qui implique qu'en se propageant, les turbulences se

retrouveront en amont et se perturberont elles-mêmes. Cette méthode est adaptée à d'autres

cas (étude d'un cisaillement pour déterminer la viscosité par exemple) mais pas à celui des

simulations qui nous intéressent (même si ce n'est pas le domaine le plus adapté pour les LGA).

Pour créer un vent, nous introduisons des particules à un certain ryhtme, qui est contrôlé

au clavier par l'utilisateur dans les expériences réalisées. Leur direction est aussi importante :

elle doit être décorrélée, aussi aléatoire que possible, pour éviter que les caractéristiques

du vent n'influencent ou ne perturbent les phénomènes en aval. Pour décorréler un signal, il suffit

de le moduler par un signal connu pour être aléatoire : nous disposons déjà de phénomènes explicitement

aléatoires au niveau de certaines configurations de collision. La technique est alors de créer des

particules allant en sens inverse du vent pour, si elles en ont le temps, frapper le mur adjacent.

Cela crée une zone de haute densité propice à de nombreuses collisions, favorisant

une répartition aléatoire et naturelle des particules,

même si elles sont créées de manière déterministe. Leur surnombre local et la configuration de la paroi

forcent ainsi un flux de particules aléatoires dans le sens désiré (en moyenne). L'entropie du modèle

leur assure une répartition naturellement équilibrée dans le temps et dans l'espace.

Le deuxième problème important concerne les autres conditions aux limites. D'abord, les parois

horizontales (supérieure et inférieure) sont "rugueuses" : le modèle le plus simple spécifie que les particules

repartent par le lien où elles étaient venues. Ensuite, la paroi de droite est totalement

"absorbante" et fait disparaitre toutes les particules. Dans la réalité,

cela correspondrait à un tuyau débouchant dans le vide sidéral, ce qui n'est pas notre intention :

une veine de soufflerie réelle maintient une densité assez homogène autour du domaine d'étude et le vent

n'est pas "avalé" d'une manière ou d'une autre. Les conditions sont réunies pour faire apparaitre

un écoulement parabolique de Poiseuille qui interfère avec le domaine d'étude comme dans l'image

de densité sur 8 bits. La densité n'est pas homogène ni linéaire autour de l'éprouvette et le phénomène

de portance que l'on veut mettre en évidence est perturbé par l'influence des parois et de la disparition

des particules, ce qui est similaire à une anisotropie de la pression dans tout le tunnel.

La solution adoptée pour l'expérience suivante (l'accumulation sur 16 bits)

est de rétablir la pression dans le tunnel

grâce à une sorte de "peigne" qui piège une partie des particules qui allaient disparaître.

De proche en proche, elles créent une pression qui s'oppose en partie à leur disparition totale :

le fluide devient plus homogène et les directions des particules sont plus diverses. Nous voyons

sur l'image de densité 16 bits que le profil n'est plus parabolique, bien que les parois rugueuses

laissent subsister de légères perturbations locales.

La pression dans le tunnel est mieux répartie et équilibrée.

Une deuxième solution pour réduire encore plus, ou anihiler, l'écoulement parabolique est de rendre les

parois glissantes pour que leur vitesse par rapport au vent ne soit pas changée.

Cette solution a par exemple été adoptée pour l'allée de von Karman dans l'exemple de

David Hanon en III.9.

Cela n'a pas été essayé dans les premiers codes car le programme ne le permettait pas encore, seules les

parois rugueuses pouvant être codées dans un octet.

En complément de la première solution, nous disposons alors d'un domaine d'étude dont la pression

et la vitesse sont homogènes et favorables pour étudier des phénomènes turbulents comme les

allées de von Karman. Dans le cas contraire, par exemple si l'écoulement

de Poiseuille subsistait, il faudrait agrandir le tunnel de manière à ce que les paraboles

n'interviennent pas substanciellement dans les mesures, ce qui augmenterait quadratiquement

les besoins de mémoire et de temps de calcul.

Pour que ces conditions aux limites soient remplies, il faut plus de flexibilité dans le programme.

La nature du modèle FHP permet d'ajouter facilement les fonctions désirées mais leur implémentation

est souvent une aventure plus complexe que l'on pourrait s'y attendre. De plus, le bon sens des

équations classiques contredit la réalité microscopique des particules : les equations d'Euler ne

traitent pas explicitement du mouvement chaotique brownien. Un bon programme de calcul FHP a donc besoin de parois

glissantes comme rugueuses et d'un contrôle sûr de la création et de la destruction des particules.

Les algorithmes vus jusqu'à présent ne permettent pas de tel contrôle sur la rugosité des parois.

III.8 : Remplissage et redimensionnement dynamique du tunnel :

Une fois le fluide en régime "stationnaire", c'est à dire lorsque tous les phénomènes transitoires

(comme les ondes de choc ou les phénomènes anisotropiques hexagonaux) ont disparu, on effectue les

mesures et on réfléchit aux calculs suivants. En d'autres termes, une grande partie des calculs a

pour seule fonction d'éliminer les transitoires. Une formule empirique : t=4*(h+l)

donne le nombre de pas de temps à calculer pour que disparaisse la plupart des ondes de choc, soit deux

à trois allers et retours de l'onde de paroi à paroi. Or les simulations les plus intéressantes sont les plus

grosses et le temps de calcul augmente très vite ; en utilisant la formule précédente, il faut environ :

N=4*(h+l)*h*l pas de calcul en tout, ou environ N=8*l^3 si h

et l sont proches. Dans ce chapitre, nous allons explorer des moyens de réduire ce temps

de calcul.

Pour commencer, nous pouvons constater que la veine de simulation FHP est souvent vide au début

de l'expérience. Il faut l pas de temps et h*l*l = hl² calculs de site

pour remplir le tunnel en particules. Ce sont autant de cycles facilement gagnés si la veine contenait déjà

des particules !

Le problème est maintenant : comment remplir le tunnel ? Il est facile de le remplir uniformément

de particules, ou avec des particules au hasard, mais d'une part c'est trop simple et d'autre part

il faut gérer le cas délicat des éprouvettes qui seraient remplies de particules. En effet, la forme

que l'on place dans le tunnel n'est pas obligatoirement "pleine" et il faut que l'algorithme de remplissage

tienne bien compte de ce cas de figure. Comme dit plus haut, un algorithme simple ne convient pas et

il faut utiliser un algorithme de remplissage "intelligent" tel qu'on le rencontre dans les logiciels de

dessin bitmap (exploration récursive ou floodfill).

La première simplification oubliait aussi que ce qui nous intéresse est d'obtenir un état le plus proche

possible du régime stationnaire. Or le cas le plus simple consomme beaucoup de temps dans la mise

en mouvement le fluide. Une possibilité serait d'utiliser une résolution statique et approximative

des équations d'Euler ou de Navier-Stokes pour "guider" le remplissage préliminaire du tunnel. La limitation

ne se situe pas dans la charge de calcul mais dans sa complexité qui augmente avec celle de la géométrie des

parois. De plus, ce n'est pas un sujet qui nous concerne dans cette étude.

Une autre méthode serait d'utiliser les modèles plus simples comme FHP-2 ou FHP-1 pour effectuer une

première passe dans le fluide. Ces modèles sont plus a priori rapides à calculer et peuvent effectuer

une première approximation,

ce qui est intéressant puisque nous abandonnons la technique de consultation de table. Nous verrons pourtant que

le calcul a une importance aussi grande que le déplacement des données ("FHPIII est memory bound") et cette

méthode ne réduit pas le nombre de mouvements de particules. Toutefois, nous avons vu dans la partie précédente

que la principale différence entre les versions du modèle FHP concernent la viscosité, ou le nombre de Reynolds

par noeud. Si nous pouvons calculer à un nombre de Reynolds plus faible, nous avons donc intérêt à réduire

le nombre de noeuds plutôt que d'augmenter la viscosité : le programme de calcul reste identique mais nous

pouvons réduire le nombre de déplacements en réduisant la taille du tunnel lors de l'amorçage du fluide.

Pour réduire le temps total de calcul, nous avons donc intérêt à commencer avec une version dont la taille

est une fraction de la taille réelle. En pratique, le programme de ce mémoire limite la largeur minimale à

256 noeuds. Nous pouvons donc amorcer le tunnel avec cette largeur, durant le temps nécessaire à la disparition

des transitoires, soit environ 2000 pas de temps. Ensuite, le tunnel est agrandi : le cas le plus simple